Combinational Logic Design

Behavioral Code:

library ieee; -- component #1

use ieee.std_logic_1164.all;

entity OR_GATE is

port( X: in std_logic;

Y: in std_logic;

F2: out std_logic

);

end OR_GATE;

architecture behv of OR_GATE is

begin

process(X,Y)

begin

F2 <= X or Y; -- behavior des.

end process;

end behv;

-------------------------------------------------------------

library ieee; -- component #2

use ieee.std_logic_1164.all;

entity AND_GATE is

port( A: in std_logic;

B: in std_logic;

F1: out std_logic

);

end AND_GATE;

architecture behv of AND_GATE is

begin

process(A,B)

begin

F1 <= A and B; -- behavior des.

end process;

end behv;

--------------------------------------------------------------

library ieee; -- top level circuit

use ieee.std_logic_1164.all;

use work.all;

entity comb_ckt is

port( input1: in std_logic;

input2: in std_logic;

input3: in std_logic;

output: out std_logic

);

end comb_ckt;

architecture struct of comb_ckt is

component AND_GATE is -- as entity of AND_GATE

port( A: in std_logic;

B: in std_logic;

F1: out std_logic

);

end component;

component OR_GATE is -- as entity of OR_GATE

port( X: in std_logic;

Y: in std_logic;

F2: out std_logic

);

end component;

signal wire: std_logic; -- signal just like wire

begin

-- use sign "=>" to clarify the pin mapping

Gate1: AND_GATE port map (A=>input1, B=>input2, F1=>wire);

Gate2: OR_GATE port map (X=>wire, Y=>input3, F2=>output);

end struct;

----------------------------------------------------------------

Test Bench for comb_ckt.vhd:

--------------------------------------------------------------------

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

entity CKT_TB is -- empty entity

end CKT_TB;

-------------------------------------------------------------------

architecture TB of CKT_TB is

-- declare the whole circuit(entity of comb_ckt.vhd) as a component

component comb_ckt is

port( input1: in std_logic;

input2: in std_logic;

input3: in std_logic;

output: out std_logic

);

end component;

-- declare all I/O ports from unit under test as signals.

-- signals are usually declared within architecture

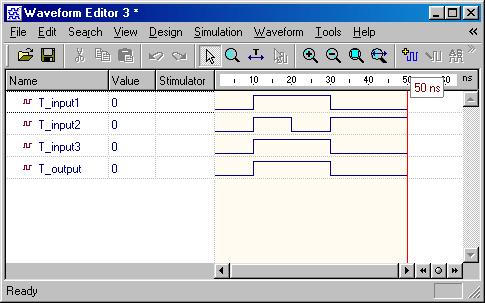

signal T_input1, T_input2, T_input3, T_output: std_logic;

begin

U_UT: comb_ckt port map (T_input1,T_input2,T_input3,T_output);

process

variable err_cnt: integer := 0;

begin

-- Test case 1

T_input1 <= '0';

T_input2 <= '0';

T_input3 <= '0';

wait for 10 ns;

assert (T_output=((T_input1 or T_input2) and T_input3))

report "Failed Case1!" severity error;

if (T_output/=((T_input1 or T_input2) and T_input3)) then

err_cnt := err_cnt +1;

end if;

-- Test case 2

T_input1 <= '1';

T_input2 <= '1';

T_input3 <= '1';

wait for 10 ns;

assert (T_output=((T_input1 or T_input2) and T_input3))

report "Failed Case1!" severity error;

if (T_output/=((T_input1 or T_input2) and T_input3)) then

err_cnt := err_cnt +1;

end if;

-- Test case 3

T_input1 <= '1';

T_input2 <= '0';

T_input3 <= '1';

wait for 10 ns;

assert (T_output=((T_input1 or T_input2) and T_input3))

report "Failed Case1!" severity error;

if (T_output/=((T_input1 or T_input2) and T_input3)) then

err_cnt := err_cnt +1;

end if;

-- Test case 4

T_input1 <= '0';

T_input2 <= '1';

T_input3 <= '0';

wait for 10 ns;

assert (T_output=((T_input1 or T_input2) and T_input3))

report "Failed Case1!" severity error;

if (T_output/=((T_input1 or T_input2) and T_input3)) then

err_cnt := err_cnt +1;

end if;

-- summary of all the tests to see if any errors

if (err_cnt=0) then

assert false report "Testbench completed successfully!"

severity note;

else

assert true

report "Something wrong, try again pls!"

severity error;

end if;

wait; -- stop running

end process;

end TB;

-------------------------------------------------------------------

configuration CFG_TB of CKT_TB is

for TB

end for;

end CFG_TB;

--------------------------------------------------------------

Behavior Simulation:

Synthesis Schematic:

Gate-level Simulation:

very helpfull sir